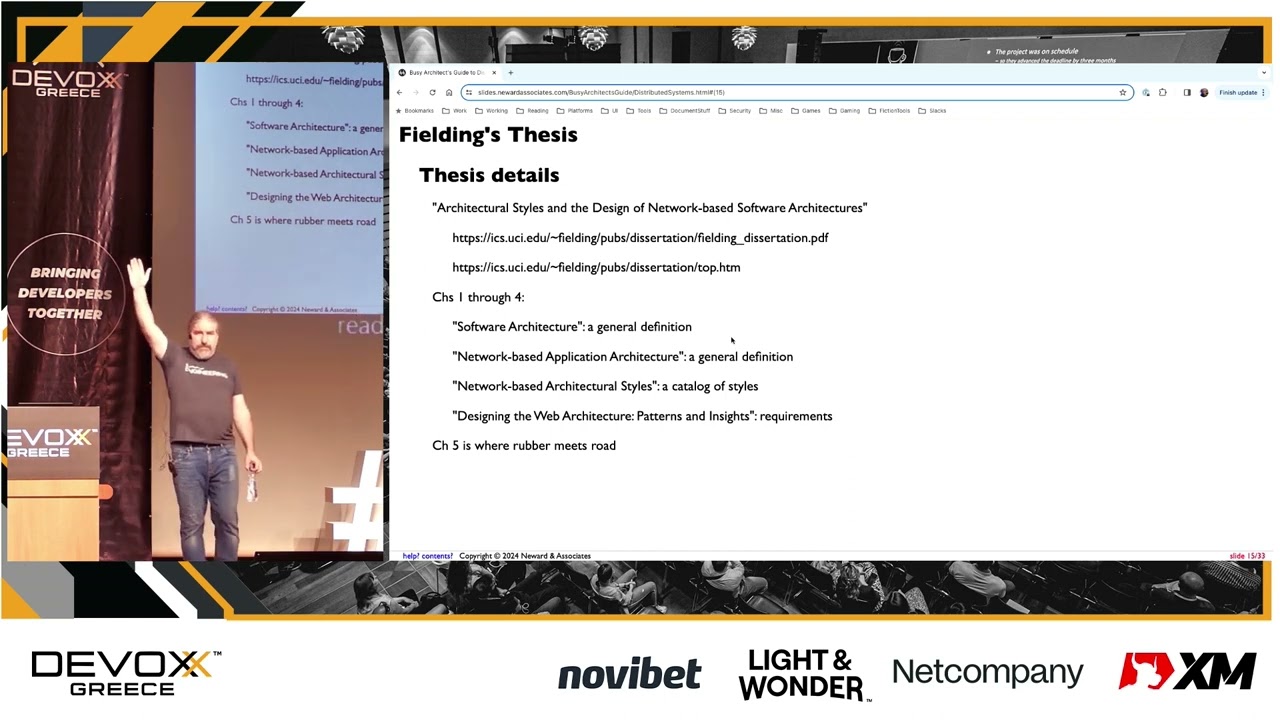

Devoxx Greece 2024 Busy Architects Guide To Distributed Systems By Ted Neward

Free Video: Busy Architect's Guide To Distributed Systems - Devoxx Greece 2024 From Devoxx ...

Free Video: Busy Architect's Guide To Distributed Systems - Devoxx Greece 2024 From Devoxx ... I'm writing 4 bit led blink code with verilog in vivado. i think my code and testbench are right, but the value of data[3:0] (which are the led output) is always in z value. can anyone help me to. Reg [31:0] out; reg [31:0] pc; initial pc <= 32'b0000000000000000000000000000000; always @ (posedge clk) begin pc <= in; out <= pc; end endmodule it is just a code for a program counter, i've set the initial value of the program counter to 0, however when i launch isim and even before running the code i checked the pc value and it's not 0.

Oscar Fernández On LinkedIn: Devoxx Greece 2024 - Taming Distributed Systems: Key Insights From ...

Oscar Fernández On LinkedIn: Devoxx Greece 2024 - Taming Distributed Systems: Key Insights From ... A net is not a legal lvalue in this context hi guys, would be very appreciative of any help anyone can give. i'm trying to design a 5bit binary to thermometer decoder for use in a 10bit segmented current dac. //verilog hdl for "lablib", "ee435" "behavioral" module ee435 (bin, thermometer). Hi all, port c on the due board has 31 bits, and my only prior experience manipulating ports was on mplab, on which each port only had 8bits, so i am not sure if my current knowledge of syntax still applies? attempted code below. Hi all, having trouble working out how to manipulate arduino due ports, as they go higher than 8bit, so couldn't workout if there was a different way of dealing with that. looking at the schematic of the arduino due, port c has 31 pins (with bits 0 30). i have attached leds from pins 44 51 (bits 12 19 on port c). i want to manipulate them, so when a variable increases in number, it changes. View verilog for multicycle demo 2.docx from n/a 101 at morse high school. fate alexis lumba red id: 820230795 verilog for multicycle demo 2 multiplexer module mux2 #(parameter wl = 32) (input [wl.

Devoxx Greece 2024 – Dimitris Doutsiopoulos

Devoxx Greece 2024 – Dimitris Doutsiopoulos Hi all, having trouble working out how to manipulate arduino due ports, as they go higher than 8bit, so couldn't workout if there was a different way of dealing with that. looking at the schematic of the arduino due, port c has 31 pins (with bits 0 30). i have attached leds from pins 44 51 (bits 12 19 on port c). i want to manipulate them, so when a variable increases in number, it changes. View verilog for multicycle demo 2.docx from n/a 101 at morse high school. fate alexis lumba red id: 820230795 verilog for multicycle demo 2 multiplexer module mux2 #(parameter wl = 32) (input [wl. Verilog codes done as part of vlsi design course. contribute to tkarthikeyan132/verilog codes development by creating an account on github. Input clk; input [31:0] in; output [31:0] out; reg [31:0] out; reg [31:0] pc; initial pc <= 32'b0000000000000000000000000000000; always @ (posedge clk) begin pc <= in; out <= pc; end endmodule it is just a code for a program counter, i've set the initial value of the program counter to 0, however when i launch isim and even before. 我正在用vivado中的verilog编写4位led闪烁代码。我认为我的代码和测试平台是正确的,但是data[3:0] (这是led的输出)的值始终是z值。 有人能帮我解决这个问题吗? 此外,运行模拟后,我的屏幕上没有输出波形。有人知道为什么会这样吗? `timescale 1ns / 1psmodule flule. Thanks for contributing an answer to stack overflow! please be sure to answer the question. provide details and share your research! but avoid … asking for help, clarification, or responding to other answers. making statements based on opinion; back them up with references or personal experience. to learn more, see our tips on writing great answers.

![[Video] Devoxx Greece On LinkedIn: Devoxx Greece 2024 - Meet Our Speakers [Video] Devoxx Greece On LinkedIn: Devoxx Greece 2024 - Meet Our Speakers](https://i0.wp.com/media.licdn.com/dms/image/D4D05AQGOp7aEpJrXAw/feedshare-thumbnail_720_1280/0/1712854798035?e=2147483647&v=beta&t=d3t8pL4P0CkVwpjS1N_qfyEx5lQUYnY-TCormgpKWw8?resize=650,400)

[Video] Devoxx Greece On LinkedIn: Devoxx Greece 2024 - Meet Our Speakers

[Video] Devoxx Greece On LinkedIn: Devoxx Greece 2024 - Meet Our Speakers Verilog codes done as part of vlsi design course. contribute to tkarthikeyan132/verilog codes development by creating an account on github. Input clk; input [31:0] in; output [31:0] out; reg [31:0] out; reg [31:0] pc; initial pc <= 32'b0000000000000000000000000000000; always @ (posedge clk) begin pc <= in; out <= pc; end endmodule it is just a code for a program counter, i've set the initial value of the program counter to 0, however when i launch isim and even before. 我正在用vivado中的verilog编写4位led闪烁代码。我认为我的代码和测试平台是正确的,但是data[3:0] (这是led的输出)的值始终是z值。 有人能帮我解决这个问题吗? 此外,运行模拟后,我的屏幕上没有输出波形。有人知道为什么会这样吗? `timescale 1ns / 1psmodule flule. Thanks for contributing an answer to stack overflow! please be sure to answer the question. provide details and share your research! but avoid … asking for help, clarification, or responding to other answers. making statements based on opinion; back them up with references or personal experience. to learn more, see our tips on writing great answers.

Devoxx Greece On LinkedIn: Devoxx Greece 2024

Devoxx Greece On LinkedIn: Devoxx Greece 2024 我正在用vivado中的verilog编写4位led闪烁代码。我认为我的代码和测试平台是正确的,但是data[3:0] (这是led的输出)的值始终是z值。 有人能帮我解决这个问题吗? 此外,运行模拟后,我的屏幕上没有输出波形。有人知道为什么会这样吗? `timescale 1ns / 1psmodule flule. Thanks for contributing an answer to stack overflow! please be sure to answer the question. provide details and share your research! but avoid … asking for help, clarification, or responding to other answers. making statements based on opinion; back them up with references or personal experience. to learn more, see our tips on writing great answers.

Devoxx Greece 2024 - Busy Architect's Guide to Distributed Systems by Ted Neward

Devoxx Greece 2024 - Busy Architect's Guide to Distributed Systems by Ted Neward

Related image with devoxx greece 2024 busy architects guide to distributed systems by ted neward

Related image with devoxx greece 2024 busy architects guide to distributed systems by ted neward

About "Devoxx Greece 2024 Busy Architects Guide To Distributed Systems By Ted Neward"

![[Video] Devoxx Greece On LinkedIn: Devoxx Greece 2024 - Meet Our Speakers [Video] Devoxx Greece On LinkedIn: Devoxx Greece 2024 - Meet Our Speakers](https://i0.wp.com/media.licdn.com/dms/image/D4D05AQGOp7aEpJrXAw/feedshare-thumbnail_720_1280/0/1712854798035?e=2147483647&v=beta&t=d3t8pL4P0CkVwpjS1N_qfyEx5lQUYnY-TCormgpKWw8?resize=91,91)

Comments are closed.